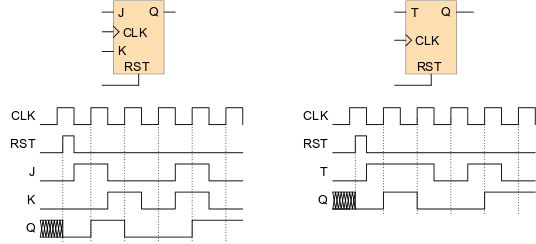

T Flip Flop Timing Diagram

In electronics a flip flop or latch is a circuit that has two stable states and can be used to store state information a bistable multivibratorthe circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. Similarly a t flip flop can be constructed by modifying d flip flop.

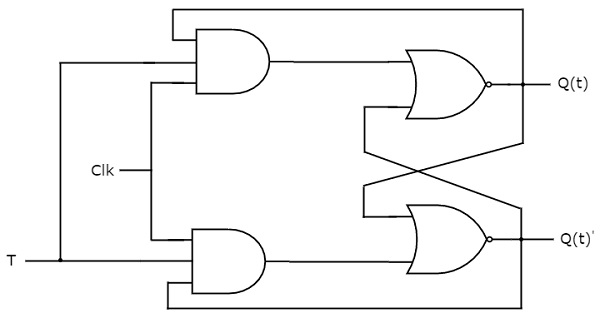

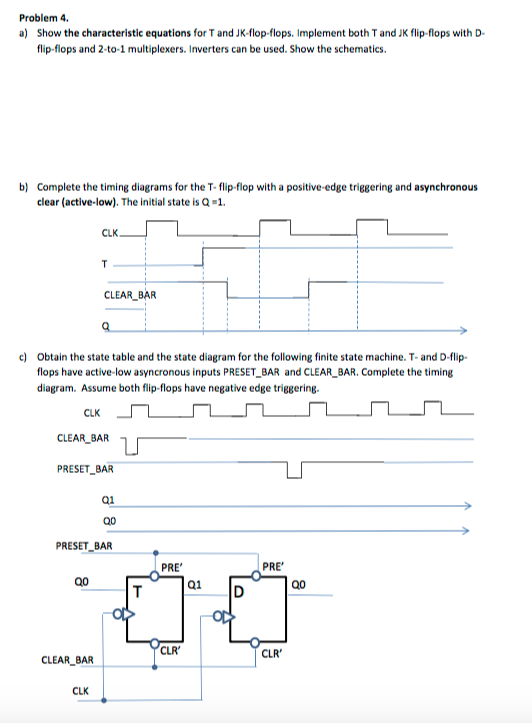

The circuit of a t flip flop constructed from a d flip flop is shown below.

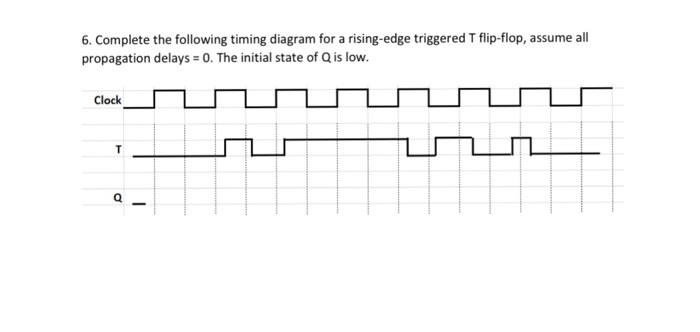

T flip flop timing diagram. We will assume an initial condition t 0 of q being low and q being high. A timing diagram illustrating the action of a positive edge triggered device is shown in fig. The circuit diagram of a t flip flop constructed from sr latch is shown below.

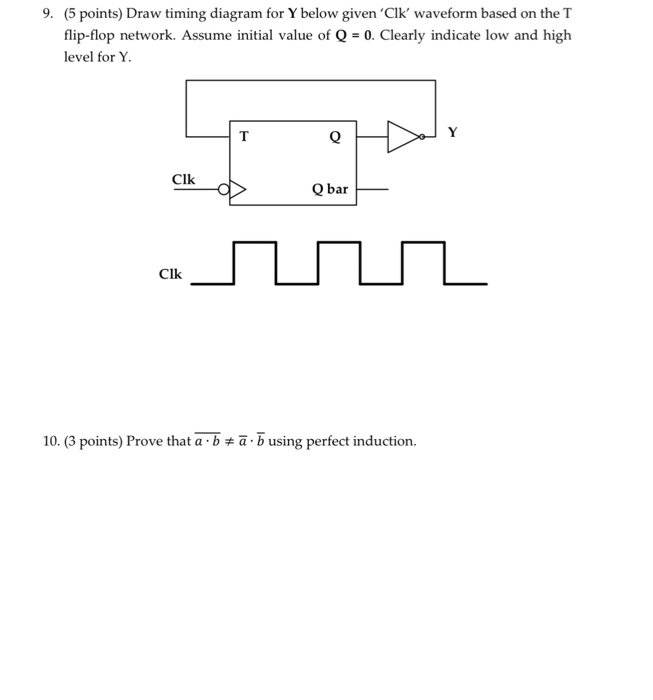

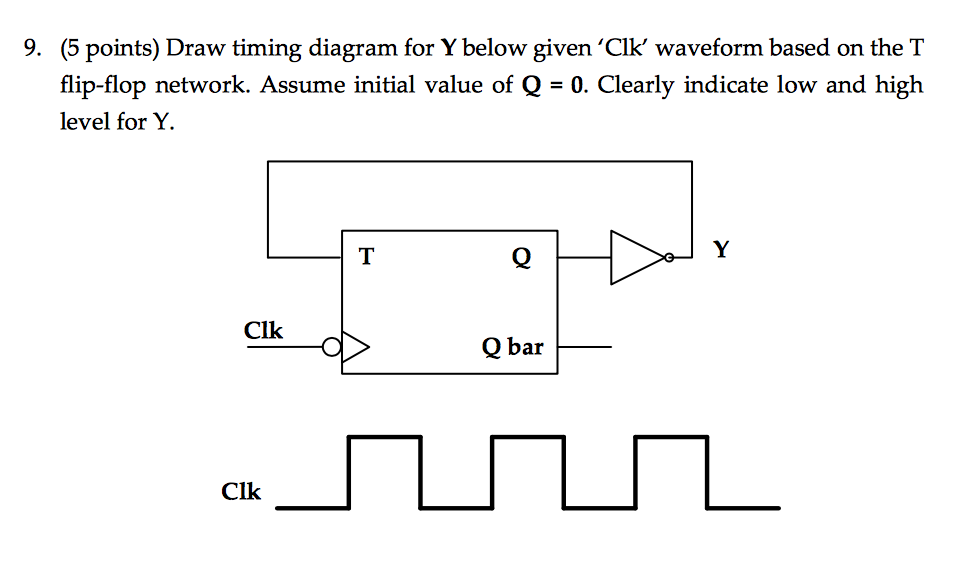

The edge triggered d type flip flop with asynchronous preset and clear capability although developed from the basic sr flip flop becomes a very versatile flip flop with many uses. Input passes to output. Enter the expected timing diagram for the signals y y q and q in figure 15.

T flip flop is termed from the nature of toggling operation. Here is my attempt so far at filling in the waveforms. Q goes high and q goes low.

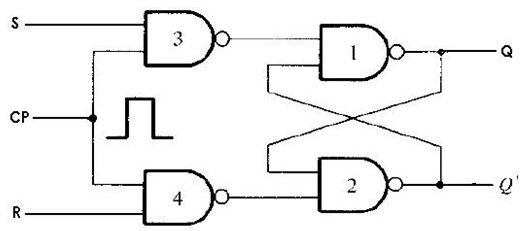

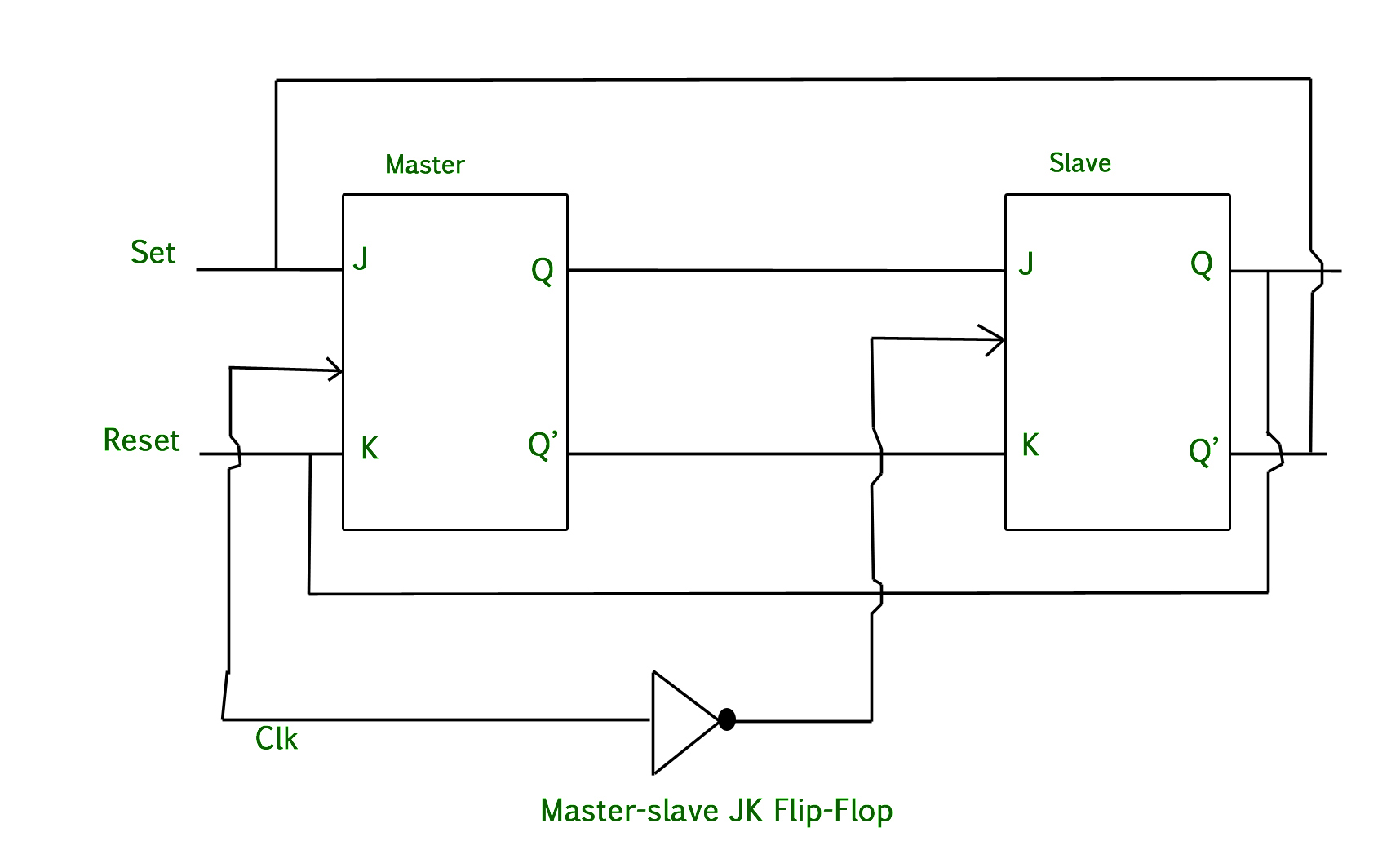

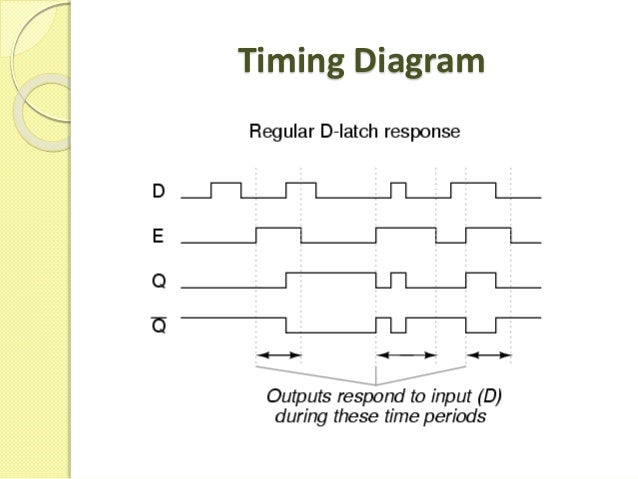

T flip flop is modified form of jk flip flop making it to operate in toggling region. Overview last lecture introduction to sequential logic and systems the basic concepts a simple example today latches flip flops edge triggered d master slave timing diagrams t flip flops and sr latches cse370 lecture 14 2 the d latch output depends on clock clock high. Draw the logic circuit implemented with gates for the sr master slave flip flop in figure 9.

Sr master slave flip flop timing diagram edge triggered flip flop. In d flip flop the output qprev is xored with the t input and given at the d input. At t 1 the toggle changes from a low to a high and the device changes state.

It is the basic storage element in sequential logicflip flops and latches are fundamental building blocks of digital. Toggle t flip flop. I think part of the solution provided is incorrect but im not positive so i thought i would ask.

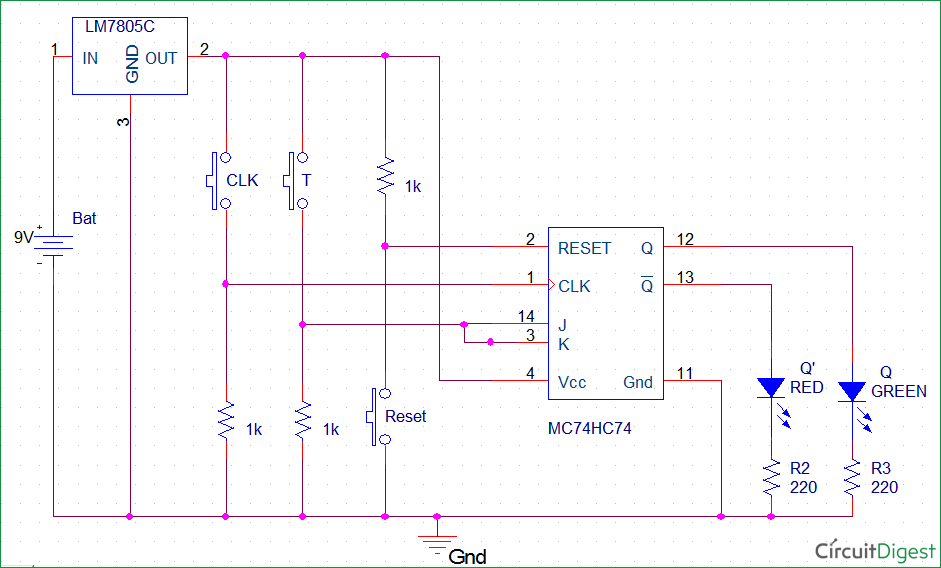

I believe the value of b provided at. Nand gate flip flop timing diagram master slave flip flop. The major applications of t flip flop are counters and control circuits.

The timing diagram in figure 3 15 view b shows the toggle input and the resulting outputs. Use nor gate flip flops. So i was doing some pre midterm studying and i was slightly confused with the operation of this circuit.

Counters In Digital Logic Geeksforgeeks

Counters In Digital Logic Geeksforgeeks

Flip Flops Registers Counters And A Simple Processor Pdf

Flip Flops Registers Counters And A Simple Processor Pdf

T Flip Flop Electronics Engineering Study Center

B Repeat Using Only Tri State Buffers Q4 A Find The Input

B Repeat Using Only Tri State Buffers Q4 A Find The Input

Flip Flops Reference Digilentinc

Flip Flops Reference Digilentinc

Types Of Flip Flop Circuits Explained Rs Jk D T

Types Of Flip Flop Circuits Explained Rs Jk D T

Timing Diagram An Overview Sciencedirect Topics

Timing Diagram An Overview Sciencedirect Topics

Intro To Flip Flops Colton Laird Portfolio

Jk Flip Flop And The Master Slave Jk Flip Flop Tutorial

Jk Flip Flop And The Master Slave Jk Flip Flop Tutorial

Digital Circuits Flip Flops Tutorialspoint

Digital Circuits Flip Flops Tutorialspoint

The Clocked T Flip Flop Timing Diagram

Solved Show The Characteristic Equations For T And Jk Flo

Solved Show The Characteristic Equations For T And Jk Flo

Flip Flops In Electronics T Flip Flop Sr Flip Flop Jk Flip

Jk Flip Flops Timing Diagram And New Flip Flop State Table

Jk Flip Flops Timing Diagram And New Flip Flop State Table

T Flip Flop Circuit Diagram Truth Table Working Explained

T Flip Flop Circuit Diagram Truth Table Working Explained

Solved Draw Timing Diagram For Y Below Given Clk Wavefo

Solved Draw Timing Diagram For Y Below Given Clk Wavefo

Digital Circuits And Systems Circuits I Sistemes Digitals

Digital Logic Master Slave Jk Flip Flop Geeksforgeeks

Digital Logic Master Slave Jk Flip Flop Geeksforgeeks

Rangkaian Sequensial Rs Flip Flop Jk Flip Flop T Flip

Rangkaian Sequensial Rs Flip Flop Jk Flip Flop T Flip

What Is The Problem Of S R Flip Flop How Can D Flip Flop

What Is The Problem Of S R Flip Flop How Can D Flip Flop

Belum ada Komentar untuk "T Flip Flop Timing Diagram"

Posting Komentar